- 您现在的位置:买卖IC网 > Sheet目录1917 > DSPIC30F2010T-20E/MM (Microchip Technology)IC DSPIC MCU/DSP 12K 28QFN

dsPIC30F2010

DS70118J-p

age

42

2011

Microchip

T

e

chnolo

g

y

Inc.

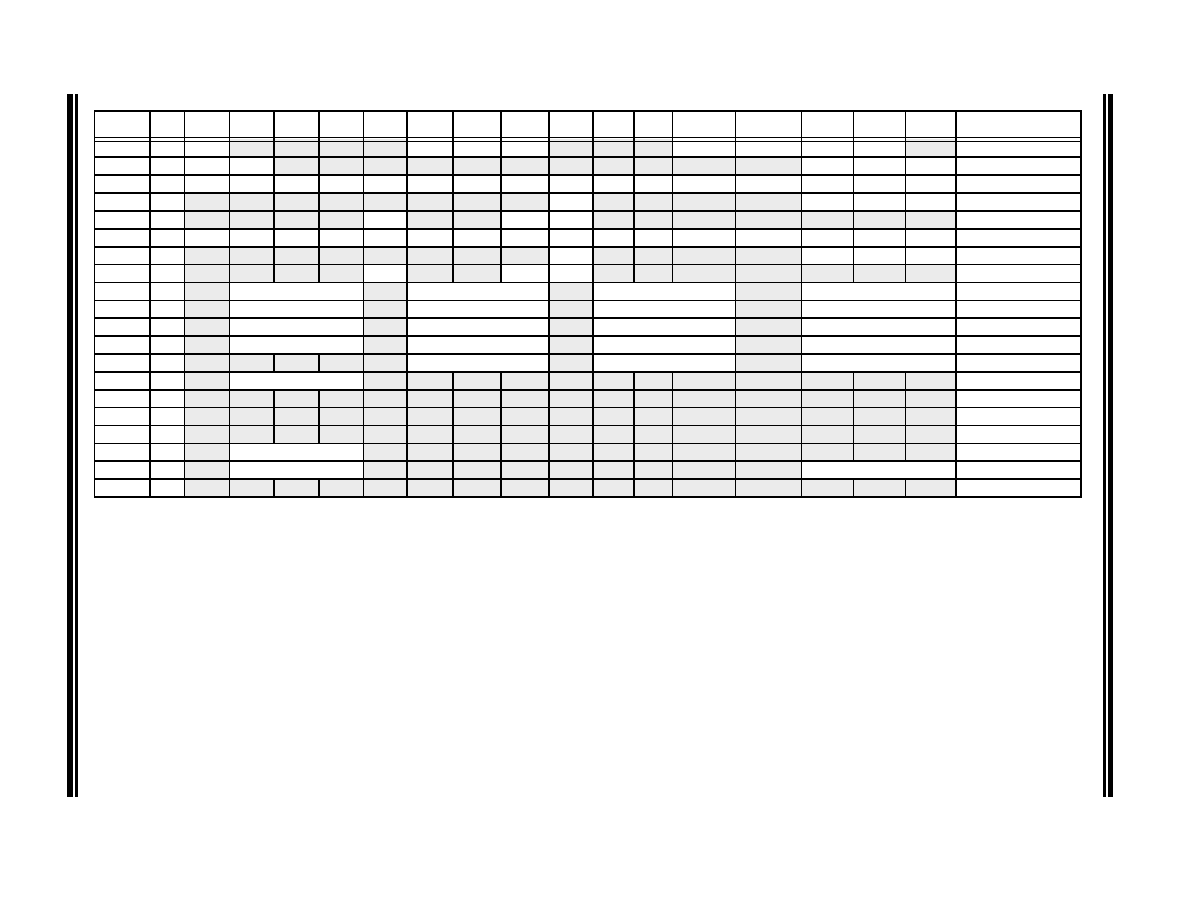

TABLE 5-2:

INTERRUPT CONTROLLER REGISTER MAP

SFR

Name

Addr.

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reset State

INTCON1

0080 NSTDIS

—

OVATE

OVBTE

COVTE

—

MATHERR

ADDRERR

STKERR OSCFAIL

—

0000 0000 0000 0000

INTCON2

0082

ALTIVT

DISI

—

INT2EP

INT1EP

INT0EP

0000 0000 0000 0000

IFS0

0084

CNIF

MI2CIF

SI2CIF

NVMIF

ADIF

U1TXIF

U1RXIF

SPI1IF

T3IF

T2IF

OC2IF

IC2IF

T1IF

OC1IF

IC1IF

INT0IF

0000 0000 0000 0000

IFS1

0086

—

—INT2IF

—

IC8IF

IC7IF

INT1IF

0000 0000 0000 0000

IFS2

0088

—

—FLTAIF

—

—QEIIF

PWMIF

—

0000 0000 0000 0000

IEC0

008C

CNIE

MI2CIE

SI2CIE

NVMIE

ADIE

U1TXIE U1RXIE

SPI1IE

T3IE

T2IE

OC2IE

IC2IE

T1IE

OC1IE

IC1IE

INT0IE

0000 0000 0000 0000

IEC1

008E

—

—INT2IE

—

IC8IE

IC7IE

INT1IE

0000 0000 0000 0000

IEC2

0090

—

—FLTAIE

—

QEIIE

PWMIE

—

0000 0000 0000 0000

IPC0

0094

—

T1IP<2:0>

—

OC1IP<2:0>

—

IC1IP<2:0>

—

INT0IP<2:0>

0100 0100 0100 0100

IPC1

0096

—

T31P<2:0>

—

T2IP<2:0>

—

OC2IP<2:0>

—

IC2IP<2:0>

0100 0100 0100 0100

IPC2

0098

—

ADIP<2:0>

—

U1TXIP<2:0>

—

U1RXIP<2:0>

—

SPI1IP<2:0>

0100 0100 0100 0100

IPC3

009A

—

CNIP<2:0>

—

MI2CIP<2:0>

—

SI2CIP<2:0>

—

NVMIP<2:0>

0100 0100 0100 0100

IPC4

009C

—

—IC8IP<2:0>

—

IC7IP<2:0>

—

INT1IP<2:0>

0100 0100 0100 0100

IPC5

009E

—

INT2IP<2:0>

—

0100 0000 0000 0000

IPC6

00A0

—

0000 0000 0000 0000

IPC7

00A2

—

0000 0000 0000 0000

IPC8

00A4

—

0000 0000 0000 0000

IPC9

00A6

—

PWMIP<2:0>

—

0000 0000 0000 0000

IPC10

00A8

—

FLTAIP<2:0>

—

QEIIP<2:0>

0100 0000 0000 0100

IPC11

00AA

—

0000 0000 0000 0000

Legend:

— = unimplemented bit, read as ‘0’

Note:

Refer to the “dsPIC30F Family Reference Manual” (DS70046) for descriptions of register bit fields.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC30F2020-30I/MMB32

IC DSPIC MCU/DSP 12K 28QFN

DSPIC30F3011-20I/P

IC DSPIC MCU/DSP 24K 40DIP

DSPIC30F3013-20I/ML

IC DSPIC MCU/DSP 24K 44QFN

DSPIC30F4011-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F4013-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F5013-30I/PT

IC DSPIC MCU/DSP 66K 80TQFP

DSPIC30F5015-30I/PT

IC DSPIC MCU/DSP 66K 64TQFP

DSPIC30F6010-20E/PF

IC DSPIC MCU/DSP 144K 80TQFP

相关代理商/技术参数

DSPIC30F2010T-20E/MMG

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 28LD 20M 12KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC30F2010T-20E/SO

功能描述:数字信号处理器和控制器 - DSP, DSC 16B MCU DSP 28LD 20MIPS 12KB FLASH RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F2010T-20E/SOG

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 28LD 20M 12KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC30F2010T-20I/MM

功能描述:数字信号处理器和控制器 - DSP, DSC 16B MCU DSP 28LD 20MIPS 12KB FLASH RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F2010T-20I/MMG

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 28LD 20M 12KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F2010T-20I/SO

功能描述:数字信号处理器和控制器 - DSP, DSC 20MHz 12KB Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F2010T-20I/SOG

功能描述:数字信号处理器和控制器 - DSP, DSC DIG SIG CONTR Lead Free Package RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

dsPIC30F2010T-30I/MM

功能描述:数字信号处理器和控制器 - DSP, DSC 16B MCU DSP 28LD 20MIPS 12KB FLASH RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT